Observação metodológica importante

O texto abaixo é uma tradução técnica integral e fiel do artigo “A Practical Guide to Connecting MCU to FPGA for Enhanced Functionality”, mantendo a estrutura lógica, argumentos, exemplos e conclusões do autor original, sem qualquer adição conceitual.

Um Guia Prático para Conectar MCU a FPGA para Funcionalidade Avançada

Microcontroladores têm sido a base dos processadores embarcados por muitos anos. De acordo com a Grand View Research, em 2024, a receita global de MCUs foi estimada em aproximadamente 36,2 bilhões de dólares, com projeções indicando crescimento para mais de 105 bilhões de dólares até 2033, a uma taxa composta de crescimento anual (CAGR) de cerca de 12,8%. De baixo custo, eficientes em termos energéticos e relativamente fáceis de usar, eles possibilitaram uma vasta gama de aplicações.

O problema surge quando os requisitos de temporização começam a ultrapassar as capacidades da execução sequencial de código. Nessas situações, uma pergunta natural emerge: este é o momento de recorrer a um FPGA?

O texto a seguir mostra onde estão os limites práticos dos MCUs, quando o escalonamento arquitetural se torna uma necessidade e como reconhecer o ponto em que a lógica de software deve ceder lugar à lógica de hardware. Este não é um artigo sobre abandonar MCUs, mas sobre expandir deliberadamente o conjunto de ferramentas quando os requisitos do sistema começam a ditar novas regras do jogo em uma aplicação específica.

Segundo o Embedded Market Study, mais de 70% dos projetos embarcados ainda dependem exclusivamente de MCUs, mesmo em aplicações com requisitos de temporização cada vez mais exigentes.

Quando um Microcontrolador Deixa de Ser Suficiente

Um microcontrolador funciona bem enquanto o sistema pode tolerar um certo grau de imprevisibilidade temporal. O problema surge quando a frequência de processamento aumenta e os requisitos de temporização deixam de ser “suaves”. Mesmo MCUs de alto desempenho, como dispositivos Cortex-M7 operando entre 300 e 600 MHz, continuam sendo arquiteturas fundamentalmente sequenciais, nas quais cada operação compete por tempo de CPU com o tratamento de interrupções, acesso a periféricos e sobrecarga do sistema.

Como observou Donald Knuth, vencedor do Prêmio Turing da ACM: “o tempo é o recurso mais precioso em um sistema computacional, e gerenciá-lo explicitamente é muitas vezes mais difícil do que gerenciar espaço”.

Como resultado, a latência deixa de ser constante e o jitter torna-se uma propriedade inerente da plataforma, e não um defeito de implementação. Nesse estágio, o projeto geralmente ainda “funciona”, mas torna-se cada vez mais difícil raciocinar sobre ele em termos de tempos de resposta garantidos. O código passa a depender de suposições implícitas de temporização que não são formalmente verificáveis. Uma pequena mudança de configuração, uma ordem diferente de interrupções ou uma tarefa adicional em segundo plano consumindo apenas 5–10% do tempo de CPU pode perturbar o comportamento do sistema de maneiras difíceis de prever e ainda mais difíceis de depurar.

A reação natural é otimizar ainda mais: desenrolamento manual de loops, abandono de abstrações, empurrar lógica para interrupções. Eventualmente, porém, torna-se claro que a limitação não está no código em si, mas no modelo de execução. Quando o sistema se torna sensível a ciclos individuais de clock, as margens de temporização se estreitam significativamente. Por exemplo, se um dispositivo externo exige um sinal de chip-select com tempos de setup e hold abaixo de 10 ns e jitter inferior a 2 ns, um MCU deixa de ser uma plataforma escalável, independentemente do esforço investido em otimização.

O Que Realmente Diferencia um FPGA de um MCU

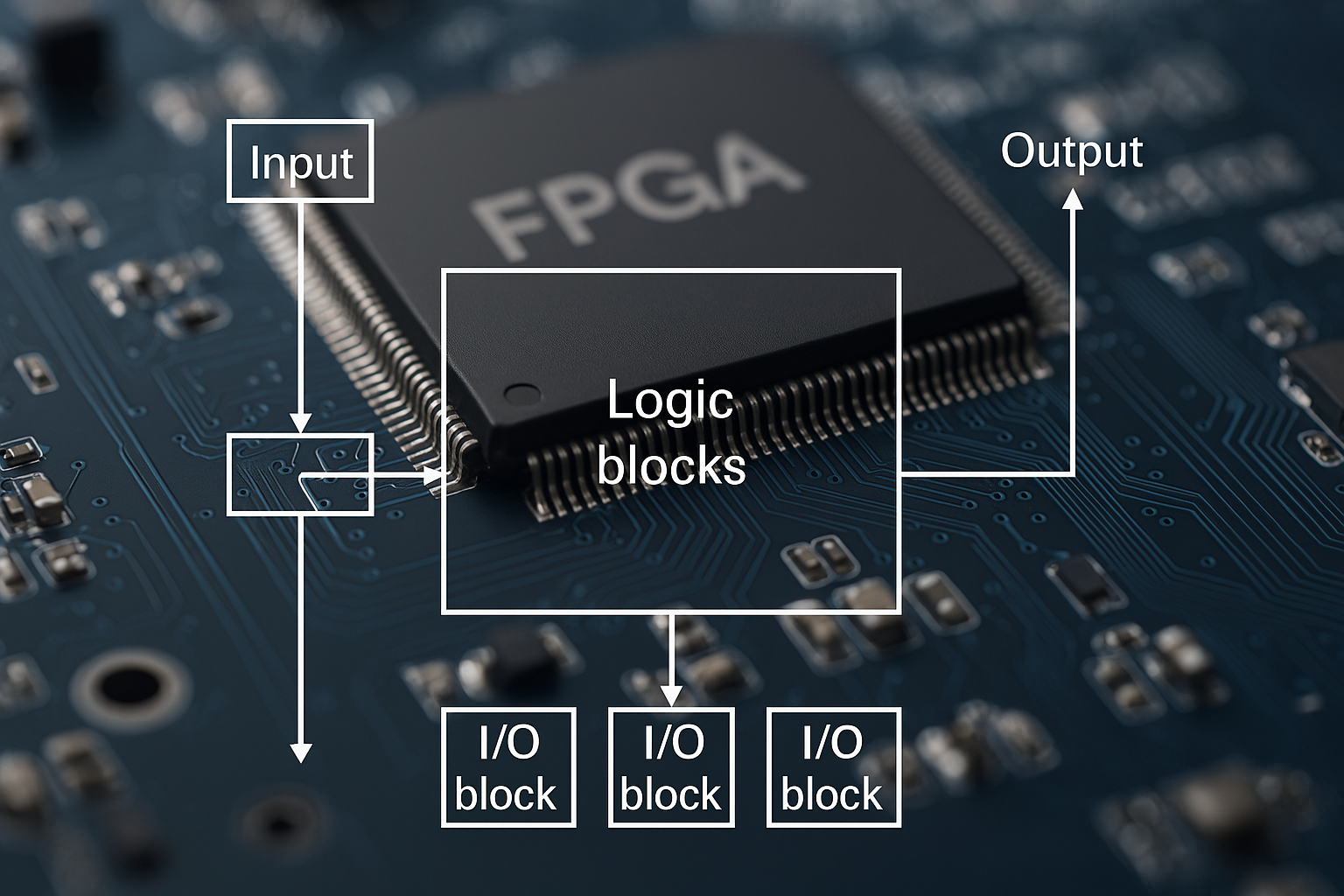

A diferença entre um MCU e um FPGA torna-se evidente no nível do que significa uma operação ser executada “no tempo certo”. Em um microcontrolador, toda função — independentemente de sua importância para o sistema — deve ser agendada dentro de um único fluxo de instruções do chip. Mesmo quando um RTOS é utilizado, a concorrência se reduz à troca de contexto, e o tempo de resposta depende do pior caso de tratamento de interrupções e de seções críticas. O determinismo, portanto, possui um caráter estatístico: ele pode ser estimado, mas não garantido para todos os caminhos de execução.

Em um FPGA, o processamento é definido como um conjunto de blocos lógicos paralelos operando simultaneamente e sincronizados por um ou mais clocks. Cada bloco possui uma latência fixa expressa em ciclos de clock, independente da atividade de outros blocos. Não existe mecanismo capaz de “roubar tempo” de outra parte da lógica, pois não há um recurso de execução compartilhado equivalente a um núcleo de CPU.

Essa abordagem permite que o tempo seja tratado como uma propriedade da própria estrutura, e não como um subproduto da execução de um programa. Se uma operação possui latência de três ciclos de clock, ela sempre terá exatamente três ciclos, sem exceções ou casos extremos. Nesse sentido, a lógica em FPGA é genuinamente um “algoritmo em silício”. O algoritmo é mapeado em registradores, lógica combinacional e interconexões, e seu comportamento temporal pode ser verificado em tempo de síntese por meio de análise de temporização.

Testes comparativos conduzidos pela Intel mostram que, enquanto sistemas baseados em MCU alcançam determinismo em aproximadamente 95–99% dos casos, FPGAs fornecem 100% de determinismo para todos os caminhos compatíveis com a temporização. Essa característica, mais do que a velocidade bruta, é o que confere vantagem aos FPGAs em sistemas de processamento de alta frequência.

Quando um FPGA Não É uma Boa Ideia

Um FPGA não é uma solução universal e, em muitos projetos, seu uso não apenas deixa de trazer benefícios, como pode degradar a qualidade geral do sistema. Se o processamento não é de tempo real rígido (hard real-time) e os requisitos de latência e jitter se mantêm dentro dos limites previsíveis de um MCU ou DSP, a migração para FPGA geralmente não se justifica tecnicamente. Isso é particularmente verdadeiro para algoritmos orientados a controle e decisão, bem como para projetos dominados por lógica condicional complexa.

Também é importante fazer uma pergunta simples, porém crítica: estamos resolvendo um problema real de temporização ou compensando uma decisão arquitetural que nunca foi a escolha correta? Em muitos cenários, um DSP especializado ou um MCU moderno com aceleradores de hardware é a escolha mais simples e apropriada.

David Patterson, um dos fundadores da arquitetura moderna de computadores como disciplina acadêmica, adverte que “complexidade arquitetural só deve ser introduzida quando elimina diretamente um gargalo fundamental”.

Outro fator importante é o custo cognitivo e técnico do desenvolvimento em FPGA. Projetar lógica de hardware exige um conjunto de habilidades diferente, ciclos de desenvolvimento mais longos e verificação rigorosa de temporização. Erros são mais difíceis de detectar e frequentemente só emergem durante a integração em hardware. Análises do IEEE indicam que projetos com FPGA alcançam seu primeiro protótipo funcional, em média, de duas a três vezes mais tarde do que projetos baseados em MCU, e que aproximadamente 40% dos erros lógicos são descobertos apenas na fase de integração de hardware.

O uso excessivo de FPGA também pode levar a uma complexidade arquitetural desnecessária. O sistema torna-se mais difícil de manter, menos adaptável a requisitos em mudança e mais propenso a problemas de integração. Se paralelismo real e determinismo rígido não forem críticos, uma plataforma mais simples geralmente resultará em uma solução final mais robusta e eficiente.

Sinais de Alerta: O Ponto de Transição em um Projeto

Os primeiros sinais claros surgem quando a arquitetura do sistema passa a ser moldada por problemas de temporização, e não pela lógica funcional. Interrupções adicionais são introduzidas, prioridades são ajustadas, atrasos manuais são inseridos e surgem trechos de código cuja única função é “manter o tempo correto”. O sistema ainda funciona, mas passa a depender de suposições frágeis.

Outro sinal ocorre quando requisitos de tempo real rígido deixam de poder ser garantidos de forma confiável. A análise de pior caso de execução torna-se cada vez mais teórica, e um único atraso pode quebrar garantias de temporização.

O sintoma mais custoso aparece quando a depuração se transforma em uma corrida contra o tempo. Erros desaparecem quando um depurador é conectado, mudam com diferentes níveis de otimização do compilador ou ocorrem apenas em condições reais de implantação.

Há também o momento em que o comportamento correto passa a depender de detalhes que não deveriam ser arquiteturalmente relevantes, como versões de compilador, pequenas mudanças em módulos não relacionados ou atualizações de bibliotecas.

O sinal final é a incapacidade de escalar sem uma mudança arquitetural. Cada novo requisito funcional se transforma automaticamente em um problema de temporização, e o projeto deixa de ser escalável.

Arquiteturas Híbridas: MCU + FPGA

Uma arquitetura híbrida combinando microcontrolador e FPGA permite explorar os pontos fortes de ambas as abordagens sem exigir um redesenho radical de todo o sistema. Não é coincidência que o mercado esteja cada vez mais adotando arquiteturas híbridas. Segundo a Omdia, mais de 60% dos novos sistemas embarcados de alto desempenho utilizam hoje uma combinação de MCU e FPGA.

O princípio fundamental é a separação clara de responsabilidades. O microcontrolador atua como camada de controle, configuração e comunicação, enquanto o FPGA lida com processamento crítico em tempo, fluxo contínuo de dados ou operações de alta frequência. O MCU gerencia estados do sistema, protocolos, lógica de decisão e interface com o usuário, enquanto o FPGA assume tarefas em que o determinismo ciclo-a-ciclo é essencial.

Na prática, vários padrões arquiteturais bem estabelecidos são utilizados, como o modelo control-plane / data-plane, a descarga parcial de algoritmos para lógica em FPGA e o uso de buffers no FPGA consumidos periodicamente pelo MCU. Um aspecto crítico é a comunicação e sincronização entre domínios de tempo diferentes, normalmente realizada por FIFOs, double buffering, sinais de handshake e limites temporais bem definidos.

SoC FPGA: A Ponte entre MCU e FPGA Clássico

Um passo natural após exceder os limites de um microcontrolador, mas antes de migrar totalmente para um FPGA puro, é o SoC FPGA. Essa arquitetura combina um processador, geralmente ARM, com lógica programável em um único dispositivo, conectados por barramentos e memória compartilhados.

Ela faz sentido quando um MCU não consegue mais atender aos requisitos de temporização, mas uma implementação totalmente em HDL seria arriscada ou complexa demais. Casos típicos incluem aquisição de dados de alta taxa, processamento digital de sinais, protocolos com temporização estrita e aceleradores de hardware personalizados.

Segundo publicações da Embedded World Conference, um SoC FPGA pode proporcionar um aumento de 5 a 20 vezes na capacidade de processamento sem exigir um redesenho completo da camada de aplicação.

Projetando Lógica para Operação em Alta Frequência

Projetar lógica em FPGA para alta frequência exige abandonar intuições derivadas da programação sequencial e adotar uma perspectiva orientada a hardware. Pipelining e paralelismo desempenham papel central, permitindo maior vazão sem encurtar caminhos críticos individuais.

O tempo, em um FPGA, não é uma abstração, mas uma propriedade concreta do projeto. Cada registrador adicional, cada decisão sobre largura de barramento e cada ordenação de operações afeta diretamente a latência e a capacidade de atender às restrições de temporização.

Equipes com mentalidade “software-first” frequentemente cometem erros previsíveis, como portar algoritmos diretamente, abusar de lógica condicional ou tratar o FPGA como um processador mais rápido. Somente ao aceitar que se está projetando uma estrutura de hardware, e não um programa, é possível explorar todo o potencial dos FPGAs.

Escalonamento Arquitetural Consciente

O escalonamento arquitetural consciente é um sinal de maturidade em engenharia. Migrar de um MCU para um FPGA não é um fracasso da arquitetura existente, nem um indicativo de superengenharia. É uma consequência natural do crescimento de requisitos.

Um FPGA não substitui o MCU; ele muda a forma como pensamos sobre tempo e paralelismo. Para alguns projetos, otimizar melhor o software será suficiente. Para outros, a decisão correta será adotar uma arquitetura híbrida ou migrar caminhos críticos para lógica personalizada.

Fonte original:

A Practical Guide to Connecting MCU to FPGA for Enhanced Functionality – InTechHouse, 2026.