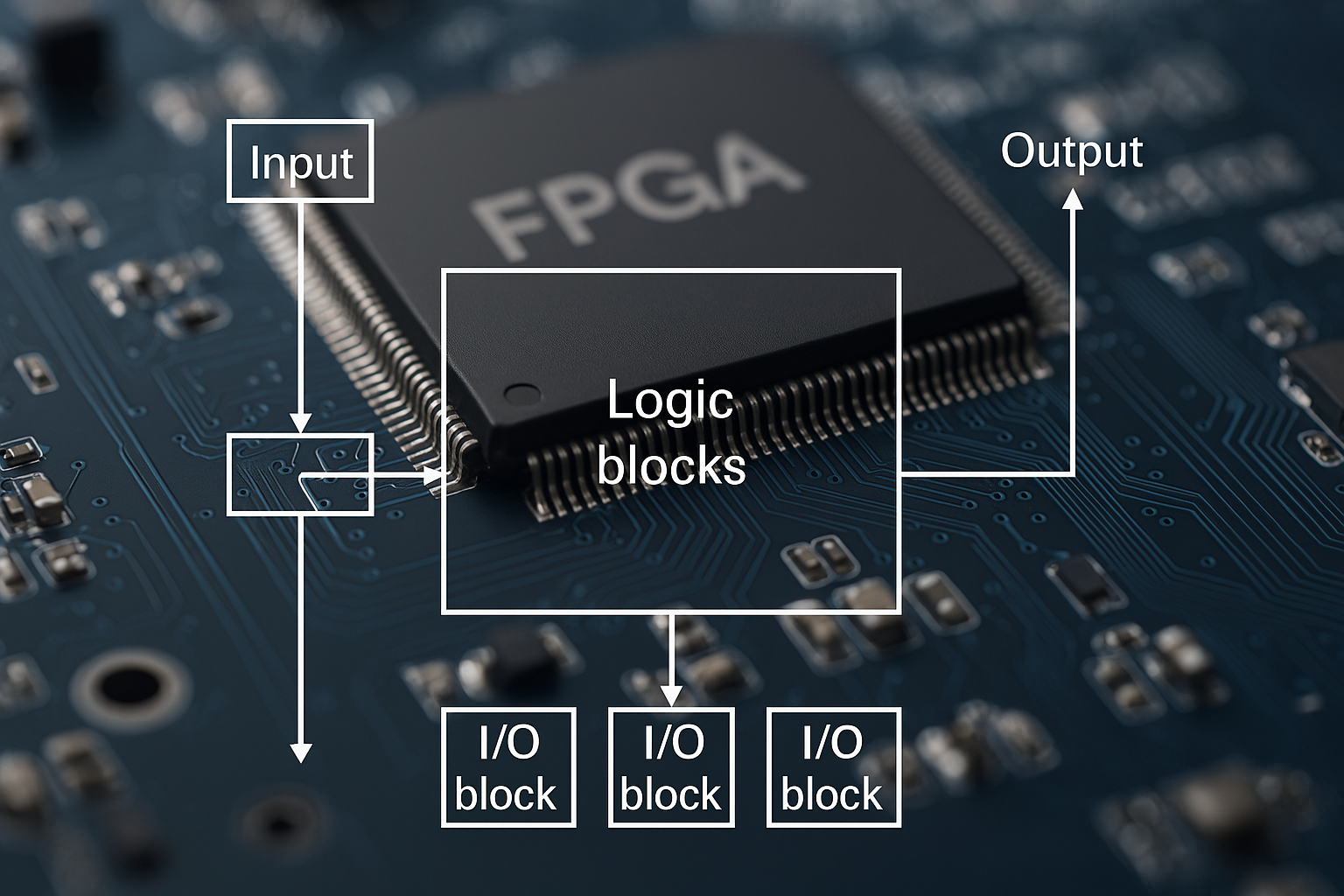

O desenvolvimento de sistemas digitais complexos exige ferramentas e linguagens que permitam a descrição precisa e eficiente do comportamento e da estrutura dos circuitos eletrônicos. Entre essas ferramentas, destacam-se as linguagens de descrição de hardware (HDLs — Hardware Description Languages), das quais Verilog e VHDL são as mais amplamente utilizadas. Essas linguagens permitem que engenheiros e pesquisadores modelem, simulem e implementem circuitos digitais em dispositivos como FPGAs (Field Programmable Gate Arrays) e ASICs (Application-Specific Integrated Circuits), representando um elo fundamental entre o mundo da eletrônica e o da computação.

Ambas as linguagens têm suas raízes na década de 1980, quando a crescente complexidade dos projetos digitais exigiu novos métodos de automação e verificação. VHDL, por exemplo, surgiu de um projeto militar financiado pelo Departamento de Defesa dos Estados Unidos, o VHSIC (Very High Speed Integrated Circuit), enquanto Verilog foi criado por uma empresa privada para facilitar o design e a verificação de circuitos integrados comerciais. Cada linguagem traz consigo características únicas que influenciam sua adoção em diferentes contextos, seja na indústria, na academia ou na pesquisa científica.

Nos últimos anos, a aplicação dessas linguagens expandiu-se significativamente, alcançando não apenas o design eletrônico tradicional, mas também áreas emergentes como a biotecnologia computacional. Um exemplo marcante é o uso de linguagens semelhantes a HDLs em pesquisas como as do MIT, que exploram a reprogramação de bactérias utilizando princípios de engenharia genética inspirados no design de circuitos digitais.

Neste artigo, exploraremos em detalhes o que são Verilog, VHDL e VHSIC, contextualizando historicamente seu surgimento, destacando suas principais características, apresentando exemplos práticos de uso e analisando como essas tecnologias estão sendo empregadas desde o desenvolvimento de FPGAs até os domínios mais inovadores da biotecnologia sintética.

O que é VHDL?

VHDL, sigla para VHSIC Hardware Description Language, é uma linguagem de descrição de hardware criada no início dos anos 1980 como parte do projeto VHSIC (Very High Speed Integrated Circuit), uma iniciativa do Departamento de Defesa dos Estados Unidos para desenvolver circuitos integrados de altíssima velocidade para aplicações militares. O objetivo era criar uma linguagem padrão e formal para documentar, simular e sintetizar circuitos digitais complexos de maneira confiável e reutilizável. Em 1987, o VHDL foi padronizado pelo IEEE como o IEEE 1076, o que permitiu sua ampla adoção pela indústria.

Diferente de linguagens de programação convencionais como C ou Python, o VHDL descreve não apenas o comportamento, mas também a estrutura física de um circuito. Isso significa que ele pode ser usado tanto para especificar a lógica funcional de um sistema (como somadores, registradores ou controladores) quanto para representar conexões físicas entre componentes em um projeto. O VHDL é fortemente tipado e baseado em sintaxe semelhante à linguagem Ada, exigindo disciplina rigorosa na definição de sinais, tipos de dados e blocos lógicos, o que o torna ideal para projetos que demandam alta confiabilidade e verificabilidade, como aplicações aeroespaciais, médicas e industriais.

Um exemplo simples em VHDL pode ser um componente que implementa uma porta lógica AND de dois bits:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity porta_and is

Port ( A : in STD_LOGIC;

B : in STD_LOGIC;

Y : out STD_LOGIC);

end porta_and;

architecture comportamento of porta_and is

begin

Y <= A and B;

end comportamento;

Esse código define uma entidade chamada porta_and com duas entradas (A e B) e uma saída (Y). A arquitetura descreve o comportamento lógico da saída como sendo o resultado da operação AND entre as duas entradas. Essa simplicidade é o ponto de partida para projetos muito mais complexos, que podem incluir sistemas embarcados completos, processadores, controladores de memória ou até mesmo interfaces de comunicação sofisticadas.

O VHDL é amplamente utilizado na indústria de semicondutores e no desenvolvimento de FPGAs. Ferramentas de síntese como Xilinx Vivado ou Intel Quartus permitem transformar um projeto em VHDL diretamente em um circuito físico que pode ser implementado em dispositivos reconfiguráveis. Além disso, o VHDL é uma escolha comum em ambientes acadêmicos e projetos que exigem documentação robusta e verificação formal, devido à sua clareza e precisão semântica.

O que é Verilog?

Verilog é uma linguagem de descrição de hardware desenvolvida em 1984 pela empresa Gateway Design Automation, com o objetivo de facilitar a modelagem, simulação e síntese de circuitos digitais. Sua proposta era oferecer uma abordagem mais simples e familiar a engenheiros acostumados com linguagens de programação como C, diferentemente do VHDL, que possui uma sintaxe mais rigorosa baseada em Ada. Verilog se popularizou rapidamente no setor comercial, sendo posteriormente padronizado como IEEE 1364 em 1995. Em 2009, a linguagem foi incorporada ao padrão SystemVerilog, uma extensão que adiciona recursos avançados de verificação e orientação a objetos.

A sintaxe do Verilog é mais enxuta e permissiva que a do VHDL, o que pode acelerar o desenvolvimento inicial, embora possa trazer desafios na legibilidade e manutenção de projetos muito complexos. Verilog também suporta modelagem de diferentes níveis de abstração: desde a descrição comportamental, passando pela descrição de transferência de registradores (register-transfer level, RTL), até o nível estrutural, onde os componentes físicos são interligados explicitamente. Esse espectro de abstrações torna Verilog uma ferramenta poderosa para o desenvolvimento iterativo de hardware.

Veja abaixo um exemplo simples de uma porta lógica AND usando Verilog:

module porta_and (

input wire A,

input wire B,

output wire Y

);

assign Y = A & B;

endmodule

Neste exemplo, o módulo porta_and recebe duas entradas (A e B) e gera uma saída Y usando a operação lógica AND. A clareza e concisão do código ilustram por que Verilog é frequentemente preferido em ciclos de desenvolvimento rápidos, startups e projetos comerciais que visam tempo reduzido de mercado.

Verilog é amplamente adotado por grandes fabricantes de FPGA, como Xilinx e Intel (anteriormente Altera), sendo compatível com ferramentas populares como Vivado, ModelSim e Synplify. Além disso, é a linguagem preferida para o design de ASICs em empresas de semicondutores e também está presente em projetos open-source relevantes, como o RISC-V, uma arquitetura de processador modular e aberta.

Outro campo onde Verilog ganha destaque é na prototipagem de sistemas heterogêneos que combinam lógica programável com software embarcado, como SoCs (System-on-Chip), onde o hardware customizado coexiste com processadores ARM. Isso permite, por exemplo, a criação de aceleradores de IA dedicados ou pipelines personalizados de processamento de sinais.

O que é VHSIC?

VHSIC é a sigla para Very High Speed Integrated Circuit — ou, em português, Circuito Integrado de Velocidade Muito Alta. Embora não seja uma linguagem de descrição de hardware por si só, o termo está intimamente ligado ao desenvolvimento do VHDL. O programa VHSIC foi uma iniciativa estratégica lançada no início da década de 1980 pelo Departamento de Defesa dos Estados Unidos com o objetivo de acelerar o desenvolvimento de circuitos integrados de altíssima velocidade para aplicações militares e aeroespaciais, como mísseis guiados, radares e sistemas de comunicação criptografada.

O contexto do programa VHSIC envolvia a necessidade de superar as limitações dos circuitos integrados convencionais, frente à crescente complexidade dos sistemas digitais e à corrida tecnológica da Guerra Fria. Para isso, o programa financiou não apenas a pesquisa em novos materiais e tecnologias de semicondutores, mas também o desenvolvimento de ferramentas e metodologias de projeto. Nesse cenário, tornou-se evidente a carência de uma linguagem padronizada e formal que pudesse descrever circuitos de maneira legível, verificável e sintetizável. Assim nasceu o VHDL — como uma subparte do projeto VHSIC — para suprir essa lacuna.

Embora o programa VHSIC em si tenha se encerrado no início dos anos 1990, seu legado é profundo. Ele não apenas influenciou o desenvolvimento de circuitos de alto desempenho que hoje encontramos em satélites, aviões e sistemas embarcados críticos, como também deu origem a um ecossistema de ferramentas de engenharia que continuam sendo fundamentais para o projeto de hardware até os dias atuais.

É importante entender que, enquanto VHDL e Verilog são linguagens, o VHSIC foi um projeto tecnológico com múltiplos objetivos — desde a criação de processos fabris até o desenvolvimento de algoritmos de automação de projeto. Seu impacto histórico mostra como a necessidade de inovação em ambientes extremos (como defesa e espaço) pode impulsionar o surgimento de tecnologias fundamentais para a indústria civil, incluindo smartphones, veículos autônomos, redes 5G e dispositivos médicos inteligentes.

Comparação entre Verilog e VHDL

Apesar de Verilog e VHDL terem finalidades semelhantes — descrever e modelar circuitos digitais — suas diferenças conceituais, sintáticas e filosóficas influenciam diretamente o fluxo de trabalho, a curva de aprendizado e a manutenção dos projetos.

Origem e Filosofia: VHDL nasceu em um ambiente militar-acadêmico, com foco em precisão formal e robustez. É fortemente tipado, o que obriga o desenvolvedor a declarar explicitamente os tipos de sinais, promovendo legibilidade e verificabilidade em projetos de alta criticidade. Por outro lado, Verilog teve origem comercial e foi projetado para ser mais direto e semelhante a linguagens como C, o que o torna mais acessível a engenheiros com formação em software. Verilog adota uma tipagem mais permissiva, o que permite uma escrita mais concisa, embora potencialmente mais propensa a erros sutis.

Sintaxe e Legibilidade: A sintaxe do VHDL é mais verbosa e estruturada. Por exemplo, um simples registrador pode exigir várias linhas de código com definições explícitas de sinais, pacotes e bibliotecas. Em contrapartida, Verilog permite descrever o mesmo componente com poucas linhas, facilitando prototipagem rápida. No entanto, essa simplicidade pode comprometer a legibilidade em grandes sistemas.

Ferramentas e Adoção: Ambas as linguagens são amplamente suportadas por ferramentas de desenvolvimento de FPGAs, como Xilinx Vivado, Intel Quartus, Synplify e ModelSim. No entanto, a indústria acadêmica e a aeronáutica tradicionalmente preferem o VHDL por sua clareza formal, enquanto empresas comerciais, startups e projetos de ASICs tendem a adotar Verilog pela agilidade de desenvolvimento. Nos últimos anos, o SystemVerilog (uma extensão de Verilog com recursos de orientação a objetos e verificação formal) vem ganhando espaço como um padrão moderno de design e verificação.

Exemplo prático: Imagine a modelagem de um contador binário de 4 bits. Em VHDL, o projeto pode levar mais tempo para ser escrito, mas o controle sobre os tipos e temporizações será mais explícito. Já em Verilog, o mesmo contador pode ser criado com meia dúzia de linhas e testado rapidamente, sendo ideal para ciclos curtos de desenvolvimento.

Portabilidade e Reutilização: O VHDL possui recursos robustos de encapsulamento e modularização que favorecem a reutilização de componentes em projetos diferentes, algo que pode ser mais limitado em Verilog puro (embora melhorado com SystemVerilog). Além disso, projetos em VHDL tendem a ser mais portáveis entre diferentes ferramentas e fornecedores.

Resumo: VHDL é ideal quando a confiabilidade e a documentação são prioritárias. Verilog brilha quando agilidade e simplicidade são desejadas. Ambos coexistem em muitos projetos, sendo até comum equipes multidisciplinares utilizarem ambas as linguagens, cada uma em diferentes partes do sistema.

Aplicações práticas: de FPGAs a bactérias programáveis

As linguagens de descrição de hardware, como VHDL e Verilog, são amplamente conhecidas por sua aplicação no desenvolvimento de FPGAs (Field Programmable Gate Arrays) e ASICs (Application-Specific Integrated Circuits). Contudo, seus princípios — descrever sistemas em termos de lógica, interconexão e comportamento paralelo — estão sendo estendidos para áreas inovadoras, como a biologia sintética e a computação molecular.

Aplicações clássicas: FPGAs e SoCs

No contexto tradicional, VHDL e Verilog são usados para projetar sistemas digitais que operam em altas velocidades, com lógica customizada, como controladores de memória DDR, interfaces SPI/I2C/UART, filtros digitais (DSP), unidades lógicas e aritméticas (ALUs) e até mesmo processadores completos, como os baseados na arquitetura RISC-V.

FPGAs oferecem uma plataforma ideal para testes e prototipagem, já que podem ser reconfigurados mesmo após a fabricação. Usando Verilog ou VHDL, um engenheiro pode implementar um decodificador de vídeo em tempo real, um algoritmo de compressão de dados ou uma unidade criptográfica dedicada. Por sua natureza paralela, os FPGAs superam CPUs tradicionais em tarefas como processamento de sinais, visão computacional e inteligência artificial embarcada.

Aplicações emergentes: Engenharia Genética e Biologia Sintética

Um campo revolucionário que vem explorando os princípios das HDLs é a biologia sintética — mais especificamente, o uso de linguagens inspiradas em Verilog para programar organismos vivos. Um dos marcos dessa aplicação foi o trabalho conduzido pelo MIT e pelo laboratório de engenharia biológica de Christopher Voigt, que desenvolveu linguagens de descrição genética para programar bactérias como E. coli.

Essas linguagens biológicas permitem descrever circuitos genéticos usando lógica digital, como portas AND, OR, NOT, flip-flops e até memórias. Em vez de sinais elétricos, os “sinais” são concentrações de proteínas ou moléculas sinalizadoras, e os “componentes” são promotores, genes e reguladores de expressão. Um exemplo é a construção de um biossensor que ativa a produção de uma proteína fluorescente somente na presença de duas substâncias específicas — algo análogo a uma porta lógica AND.

Um projeto de destaque é o Cello (por “Cell logic”), uma linguagem inspirada em Verilog para programar circuitos genéticos. O usuário escreve o comportamento desejado em uma sintaxe semelhante a HDL, e o compilador Cello traduz esse código para sequências de DNA que podem ser inseridas em bactérias. Os microrganismos resultantes são programados para realizar funções como detecção de doenças, liberação de medicamentos ou resposta a estímulos ambientais.

Convergência entre Engenharia Elétrica e Biotecnologia

A união entre engenharia eletrônica e biotecnologia está criando uma nova fronteira chamada bioeletrônica, onde sensores implantáveis, dispositivos wearable e sistemas de monitoramento se integram com circuitos programáveis. Os engenheiros que dominam VHDL e Verilog já têm a base lógica necessária para entender e criar algoritmos genéticos sintéticos, pois a lógica digital serve como modelo direto para muitos processos celulares programáveis.

Assim, o conhecimento em linguagens HDLs não apenas capacita profissionais para trabalhar com sistemas embarcados e FPGAs, mas também abre portas para áreas multidisciplinares, onde biologia, computação e eletrônica convergem para transformar a medicina, a agricultura e o meio ambiente.

Conclusão

Verilog, VHDL e o projeto VHSIC representam mais do que ferramentas técnicas — são pilares de uma revolução contínua no desenvolvimento de sistemas digitais e na maneira como engenheiros concebem, testam e implementam circuitos. Desde aplicações clássicas em FPGAs e ASICs até a programação de organismos vivos, essas linguagens mostram a incrível capacidade da engenharia de cruzar fronteiras e expandir seu impacto para além do silício.

A escolha entre Verilog e VHDL depende fortemente do contexto, das exigências do projeto e da familiaridade da equipe com a linguagem. Enquanto o VHDL oferece rigor formal e é amplamente adotado em setores onde a confiabilidade é inegociável, como aeroespacial e defesa, o Verilog brilha por sua agilidade, concisão e fluidez, sendo ideal para prototipagem rápida e projetos comerciais. Em paralelo, os conceitos estruturais e lógicos dessas linguagens estão sendo reaproveitados para programar materiais vivos, como bactérias, expandindo o domínio da computação para o nível molecular.

O engenheiro do futuro não será apenas um programador de sistemas eletrônicos, mas também um designer de comportamento — seja em chips, organismos ou até sistemas híbridos entre biologia e computação. Entender Verilog e VHDL, portanto, é não apenas dominar o passado e o presente do hardware digital, mas também preparar-se para os horizontes inovadores da computação programável em todas as suas formas.